US007068101B2

# (12) United States Patent Sa'ed et al.

(10) Patent No.: US 7,068,101 B2

(45) **Date of Patent: Jun. 27, 2006**

# (54) ADAPTIVE PREDISTORTION FOR A TRANSMIT SYSTEM

(75) Inventors: Aryan Saèd, Ottawa (CA); Jean-Paul

Rene DeCruyenaere, Ottawa (CA)

(73) Assignee: Icefyre Semiconductor Corporation

(CA)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 148 days.

(21) Appl. No.: 10/613,372

(22) Filed: Jul. 3, 2003

(65) Prior Publication Data

US 2005/0001674 A1 Jan. 6, 2005

(51) **Int. Cl. H03F 1/26**

(2006.01)

See application file for complete search history.

# (56) References Cited

### U.S. PATENT DOCUMENTS

| 5,880,633    | Α  | * | 3/1999  | Leizerovich et al 330/84 |

|--------------|----|---|---------|--------------------------|

| 6,072,364    | Α  |   | 6/2000  | Jeckeln et al 330/149    |

| 6,342,810    | В1 |   | 1/2002  | Wright et al.            |

| 2001/0054974 | A1 |   | 12/2001 | Wright                   |

| 2002/0034260 | A1 |   | 3/2002  | Kim                      |

2002/0101937 A1 8/2002 Antonio et al.

#### FOREIGN PATENT DOCUMENTS

| EP | 1 313 278   | 5/2003 |

|----|-------------|--------|

| WO | WO 01/05026 | 1/2001 |

| WO | WO 01/56146 | 8/2001 |

#### OTHER PUBLICATIONS

Michael Faulkner; Adaptive Linearization Using Predistortion—Experimental Results, IEEE Transactions on Vehicular Technology; May 1994; pp 323–332; vol. 43, No. 2.

Primary Examiner—Steven J. Mottola (74) Attorney, Agent, or Firm—Kirkpatrick & Lockhart Nicholson Graham LLP

# (57) ABSTRACT

Systems, methods, and devices relating to the provision of deliberate predistortion to an input signal to compensate for distortions introduced by an amplifier subsystem. An input signal is received by a predistortion subsystem which applies deliberate predistortions to the input signal to arrive at a predistorted signal. The predistorted signal is received by an amplifier subsystem which decomposes the signal, processes the decomposed signal, and then recombines the components to arrive at a system output signal. The predistortion subsystem adaptively adjusts the predistortions based on characteristics of the system output signal. A feedback signal, a replica of the system output signal, is used in updating lookup table entries used to determine the predistortion.

# 40 Claims, 7 Drawing Sheets

<sup>\*</sup> cited by examiner

# ADAPTIVE PREDISTORTION FOR A TRANSMIT SYSTEM

#### FIELD OF THE INVENTION

The present invention relates generally to power amplification systems and is specifically applicable but not limited to power amplification systems using a Chireix architecture.

#### BACKGROUND TO THE INVENTION

The recent revolution in communications has caused a renewed focus on wireless technology based products. Mobile telephones, handheld computers, and other devices now seamlessly communicate using wireless technology. 15 One component that forms the core of such technology is the amplifier. Wireless devices require high efficiency amplifiers to not only extend the range of their coverage but also to conserve the limited battery power that such devices carry.

One possible architecture which may be used for such a 20 power amplifier is called a Chireix architecture. Named after Henry Chireix who first proposed such an architecture in the 1930s, the Chireix architecture has fallen out of favor due to its seemingly inherent limitations. However, it has recently been revisited as it provides some advantages that other 25 architectures do not have.

While the Chireix architecture provides some advantages, the process which the input signal undergoes also introduces some drawbacks. Specifically, distortions are introduced into the signal by the components in the Chireix based amplifier/modulator system. These distortions may also change over time and may therefore lead to a time-varying "drift" or change in the signal. Such distortions, timevarying or not, have led to problems that are not only inconvenient but expensive as well.

Based on the above, there is therefore a need for an amplifier system which provides the benefits of a Chireix based amplifier but which also compensates for or avoids the distortions which a Chireix based amplifier introduces. Such an amplifier system should adjust to differing conditions, preferably with little or no user intervention. It is therefore an object of the present invention to provide alternatives which mitigate if not overcome the disadvantages of the prior art.

# SUMMARY OF THE INVENTION

The present invention provides systems, methods, and devices relating to the provision of deliberate predistortion to an input signal to compensate for distortions introduced 50 by an amplifier subsystem. An input signal is received by a predistortion subsystem which applies deliberate predistortions to the input signal to arrive at a predistorted signal. The predistorted signal is received by an amplifier subsystem which decomposes the signal, processes the decomposed 55 signal, and then recombines the components to arrive at a system output signal. The predistortion subsystem adaptively adjusts the predistortions based on characteristics of the system output signal. A feedback signal, a replica of the system output signal, is used in updating lookup table entries 60 used to determine the predistortion.

In a first aspect, the present invention provides a system for processing an input signal, the system comprising:

an adaptive predistortion subsystem for receiving said input signal and for producing a predistorted signal by 65 applying a deliberate predistortion to said input signal;

- a signal processing subsystem receiving and processing said predistorted signal and producing a system output signal, wherein

- said predistortion subsystem distorts said input signal to compensate for distortions in said system output signal;

- said signal processing subsystem decomposes said predistorted signal into separate components, each of said separate components being processed separately;

- said processing subsystem combines said components after processing to produce said system output signal;

- said deliberate predistortion applied to said input signal by said adaptive predistortion subsystem to produce said predistorted signal is adjusted based on characteristics of said system output signal and said input signal.

In a second aspect the present invention provides a method of processing an input signal to produce a system output signal, the method comprising:

- a) receiving said input signal;

- b) applying a deliberate predistortion to said input signal to result in a predistorted signal;

- c) decomposing said predistorted signal into at least two component signals;

- d) combining said at least two component signals to produce said system output signal;

- e) adjusting said deliberate predistortion based on said characteristics of said system output signal.

In a third aspect the present invention provides an adaptive predistortion subsystem for use with a signal processing system which produces a system output signal, the predistortion subsystem comprising:

determining means for determining a deliberate predistortion to be applied to an input signal;

adjustment means for applying said deliberate predistortion to said input signal;

update means for periodically updating said determining means based on characteristics of said system output

# BRIEF DESCRIPTION OF THE DRAWINGS

A better understanding of the invention will be obtained by considering the detailed description below, with refer-45 ence to the following drawings in which:

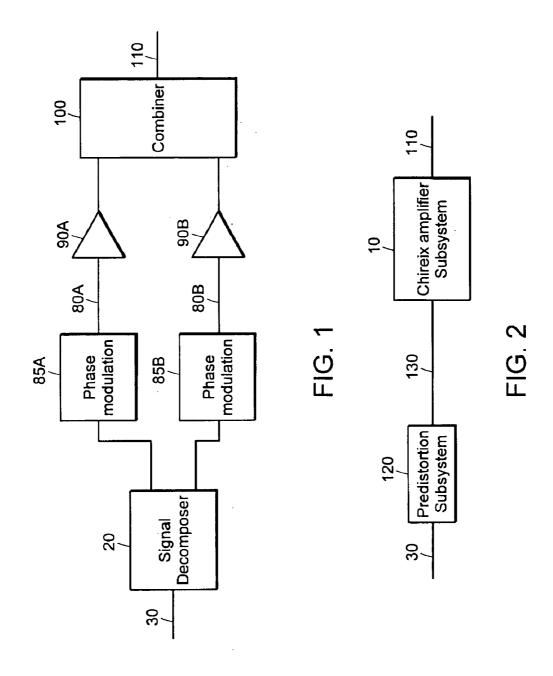

FIG. 1 is a block diagram of a Chireix architecture amplifier subsystem;

FIG. 2 is a block diagram of an amplifier system using the subsystem of FIG. 1 and a predistortion subsystem;

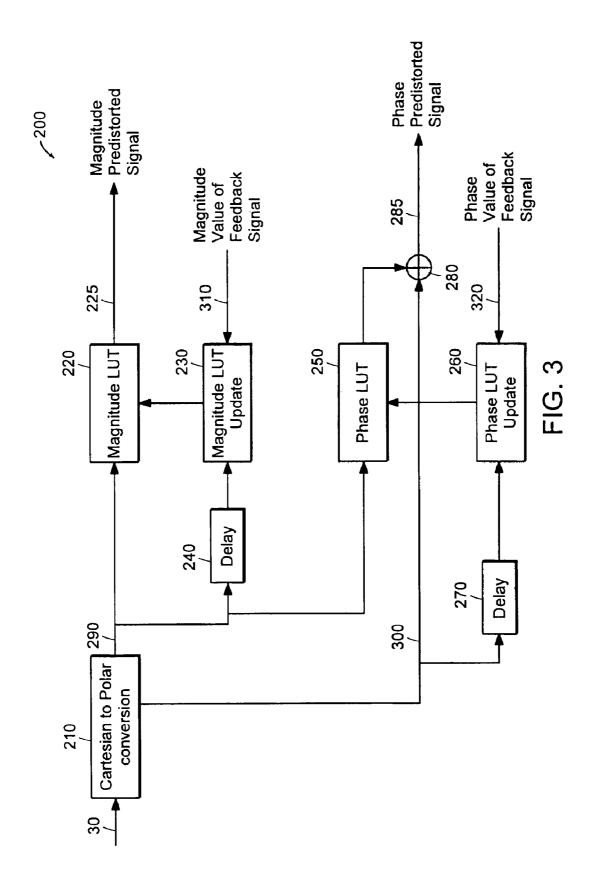

FIG. 3 is a detailed block diagram of the internal components of the predistortion subsystem;

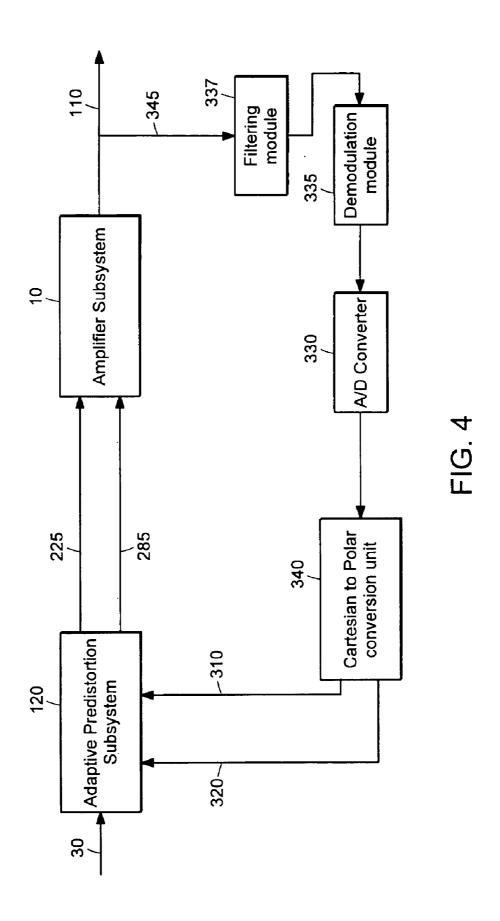

FIG. 4 illustrates the amplifier system of FIG. 2 and incorporating a feedback signal used by the predistortion subsystem of FIG. 3;

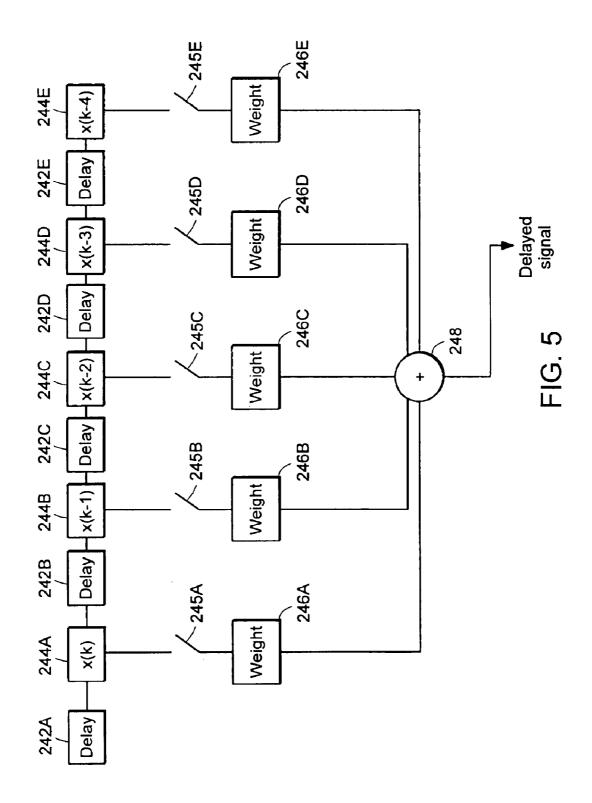

FIG. 5 is a block diagram of a delay line circuit which may be used in the system of FIG. 4;

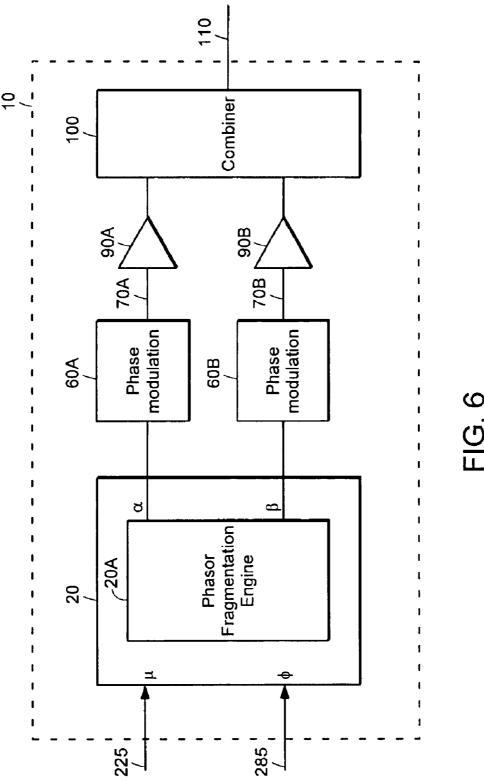

FIG. 6 is a detailed block diagram of one embodiment of a Chireix amplifier subsystem;

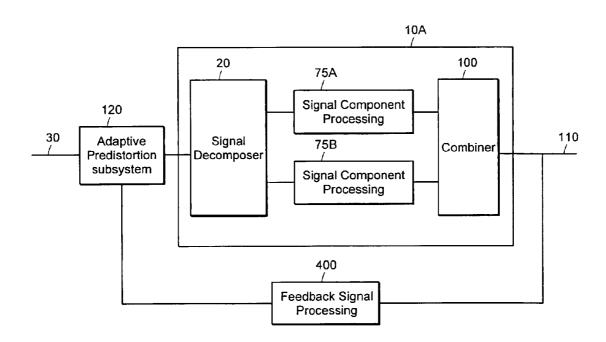

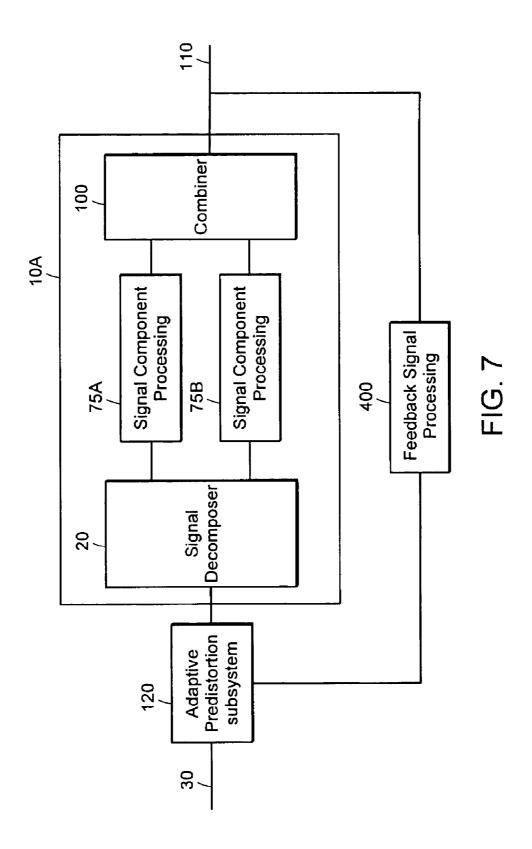

FIG. 7 is a block diagram of a signal processing system according to another embodiment of the invention; and

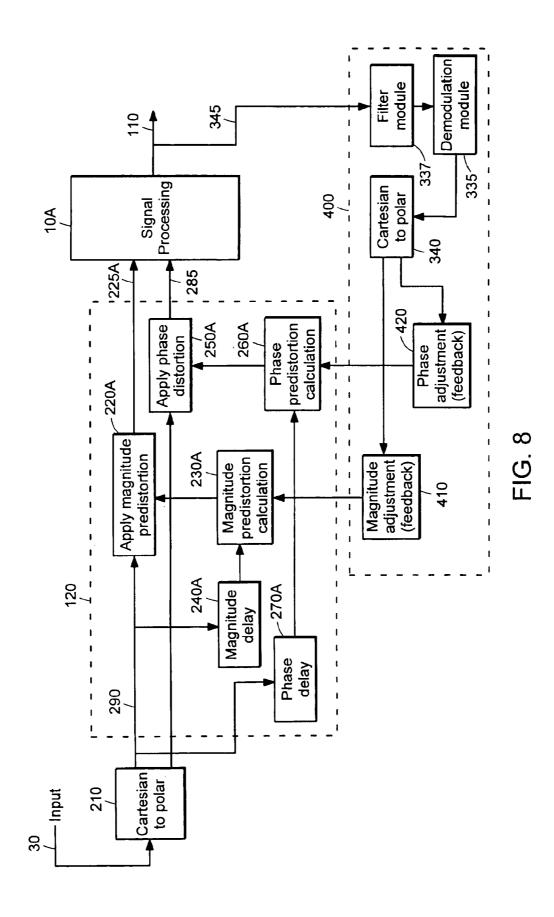

FIG. 8 is a detailed block diagram of a system incorporating the feature shown in FIGS. 3, 4 and 7.

# DETAILED DESCRIPTION

For clarity, the following terms are to be used with the following definitions:

AM (amplitude modulation) refers to the AM of an RF (radio frequency) signal and is equal to the magnitude of the RF signal's complex base band equivalent

PM (phase modulation) refers to the PM of an RF signal and is equal to the phase of the RF signal's complex 5 base band equivalent.

Referring to FIG. 1, a block diagram of a Chireix architecture amplifier subsystem 10 is illustrated. A signal decomposer 20 receives an input complex baseband signal 30. Phase modulated signals 80A, 80B are produced after 10 the decomposed output of the decomposer 20 are phase modulated by phase modulation circuitry 85A, 85B. These phase modulated signals 80A, 80B are received by power amplifiers 90A, 90B. The phase modulated signals are thus amplified by the power amplifiers 90A, 90B and are received 15 by a signal combiner 100. The system output signal 110 (an RF signal corresponding to the input baseband signal 30) is output from the combiner 100 and is an amplified and modulated version of the input signal 30. Phase modulation of the phase modulated signals 80A, 80B is executed by the 20 defined as any deliberate distortion which has been introsignal decomposer 20. The input signal 30 is separated into at least two components and these at least two components, after phase modulation, are the signals  $80\mathrm{A},\,80\mathrm{B}$

As noted above, the Chireix architecture amplifier subsystem 10 has been known to introduce distortions in the 25 system output signal 110. To compensate for such distortions, a predistortion subsystem 120 is provided. Referring to FIG. 2, the predistortion subsystem 120 receives the input signal 30 and produces a predistorted signal 130. The predistorted signal 130 is received by the 30 amplifier subsystem 10. The amplifier subsystem then produces the system output signal 110.

The distortions for which the predistortion subsystem is to compensate may come as a phase distortion, a magnitude distortion, or as a combination of both. It has been found 35 that, without predistortion, the system output signal 110 has an amplitude modulation (AM) that is not equal to the expected and desired AM. Furthermore, the phase modulation (PM) of the system output signal 110, if predistortion is Experiments have found that the AM distortion or error (magnitude distortion) depends on the AM of the input signal. Also, it has been found that the PM distortion (or phase distortion) depends on the AM of the input signal.

As noted above, one solution to the above issues is to 45 predistort the input signal as detailed in FIG. 2. Further details on this approach can be found in co-pending application entitled Predistortion Circuit For a Chireix Power Amplifier Transmit System and filed with the US Patent and Trademark Office, the whole of which is incorporated herein 50 by reference. While the predistortion solution does work, it is not as robust and as fault tolerant as may be desirable. An adaptive predistortion subsystem 200, as illustrated in FIG. 3, would compensate for conditions and for other distortions which the system output signal may have.

Referring to FIG. 3, a block diagram of such an adaptive predistortion subsystem is illustrated. The adaptive predistortion subsystem 200 of FIG. 3 may be used in place of the predistortion subsystem 120 of FIG. 2.

While an analog implementation of the subsystem 200 is 60 possible, it has been found that a digital implementation was simpler to achieve. As such, the following description assumes that the input signal 30 is a digital signal having a digital representation of the desired AM and its PM of the output RF signal. Digital AM/AM predistortion modifies the 65 magnitude of the complex digital input signal such that the RF output signal has the desired AM, despite the distortion.

Digital AM/PM predistortion modifies the phase of the complex digital input signal such that the RF output has the desired PM, despite the distortion.

As can be seen in FIG. 3, multiple components are involved in the adaptive predistortion subsystem 200: a Cartesian to polar conversion unit 210, a magnitude value lookup table (LUT) block 220, a magnitude update block 230, a magnitude delay block 240, a phase value lookup table (LUT) block 250, a phase value update block 260, a phase delay block 270, and an adder 280. The digital input signal 30 is converted by the conversion unit 210 from Cartesian coordinates to polar coordinates. The magnitude of the converted signal is then received and used by the lookup table blocks 220, 250 to determine the proper amount of predistortion to be applied. The phase lookup table 250 adds the phase distortion to the converted signal by way of the adder 280. The predistorted signal is then passed on to the amplifier subsystem 10.

It should be noted that the predistortion modification, duced to the input signal to change at least the phase or magnitude of the input signal, can take many forms. FIG. 3, provided merely for illustrative purposes, depicts two types of predistortion—phase predistortion and magnitude predistortion. These two types, separately or together, can make up the predistortion modification. In some applications, only a magnitude type predistortion modification may be required while in others only a phase type predistortion modification is required. In the embodiment explained here, the two types of predistortion, together comprise the predistortion modification.

To account for changing conditions and to acquire appropriate LUT entries, a feedback mechanism is employed to adjust or adapt the lookup table entries in lookup table blocks 220, 250. Delay blocks 240, 270 ensure that the feedback sample is mated with the proper value of the input signal waveform when processing and updating the lookup table entries in lookup table blocks 220, 250.

The conversion unit 210, while present, is not necessary not present, deviates from the expected and desired PM. 40 but merely convenient and makes the predistortion easier to accomplish. As is well known, signal representations using Cartesian coordinates take the form of z=x+j y where x and y are the real and imaginary components. Polar coordinates take the form of  $z=Ae^{j\varphi}$  where the magnitude of the signal is A and its phase is  $\varphi$ . Since both the magnitude and the phase of the signal is to be modified by the predistortion subsystem, it is clearly more convenient to accomplish this if the signal were in polar coordinates. Again as is well known,  $A=(x^2+y^2)^{1/2}$  while  $\phi=\tan^{-1}(y/x)$ . Once the signal has been converted into polar coordinates, adjusting the magnitude is as simple as replacing the digital representation of A by another number. Similarly, the phase can be adjusted by adding a phase correction to the phase of the signal.

> After the digital input signal is received and converted by 55 the conversion unit 210, the signal is now represented by two values—a magnitude value 290 and a phase value 300. FIG. 3 shows the different signal paths followed by these values—one path for the magnitude value 290 and a second path for the phase value 300.

As noted above, the magnitude value 290 can be easily replaced by the predistorted magnitude value. This is done by way of magnitude lookup table block 220. The lookup table internal to the magnitude lookup table block 220 represents an input/output relationship with the input being the undistorted magnitude and the output being the predistorted signal magnitude. Thus, if the magnitude LUT block 220 has a table entry with an input value of 0.5 and an output

value of 0.4, then if the undistorted magnitude value received by the magnitude LUT block 220 is 0.5, then this value is replaced with 0.4 as the output of the magnitude LUT block 220. Based on the LUT (lookup table) entries, the magnitude of the unidistorted signal is therefore replaced 5 with the desired predistorted magnitude.

Similar to the above, the phase value of the converted input signal is adjusted as well. As can be seen in FIG. 3, the magnitude value 290 is also received by the phase lookup table block 250. The phase lookup table block 250, based on 10 the magnitude value, determines the proper amount of phase adjustment and adds this phase adjustment to the phase value 300 by way of the adder 280. The phase lookup table block 250 also has a lookup table resident within the phase LUT block 250 that details the appropriate phase adjust- 15 ments for given magnitude values.

While the above described magnitude LUT replaces a desired value for the received magnitude, other implementations are possible. Instead of a direct replacement value, received magnitude. This corrective value can, depending on the implementation, be an additive or a multiplicative corrective value.

The adaptive predistortion subsystem 200 in FIG. 3 is adaptive in that the values of the lookup table entries in the 25 formulae (n being one table address and n+1 being another lookup table (LUT) blocks 220, 250 change over time to account for changing conditions or for acquiring appropriate LUT entries. This adaptability is implemented by way of a feedback signal tapped from the system output signal 110. Referring to FIGS. 3 and 4, two feedback signals, a mag- 30 nitude feedback signal 310 and a phase feedback signal 320, are received by the magnitude value update block 230 and by the phase value update block 260 respectively. These two feedback signals result from processing of the system output signal 110 by the analog/digital (A/D) converter 330, the 35 Cartesian to polar conversion unit 340, demodulation module 335, and filtering module 337. As can be seen in FIG. 4, the system output signal (an analog signal) is tapped and this tapped signal 345 is received by the A/D converter 330 for conversion from an analog to a digital signal.

After conversion to a digital signal, the feedback signal is converted from Cartesian to polar coordinates by the conversion unit 340. The tapped signal 345 is thus represented by the two feedback signals—the magnitude feedback signal 310 and the phase feedback signal 320. As mentioned above, 45 both these feedback signals are received by their respective update blocks 230, 260.

Once the two digital feedback signals are received, they are then compared with the delayed input signal coming from the delay blocks 240, 270. The updated values for the 50 LUT entries are then calculated and entered into their respective lookup tables. It should be noted that the comparison may be done by subtracting the feedback signals from the delayed input signal.

To further elaborate on the above process, the update 55 process is dependent on the difference between the tapped system output signal 345 and the input signal 30. This difference is, of course, taken after both signals are in polar coordinates. The magnitude and phase errors are defined as:

$$\begin{split} e_m(k) &= |z(k)| - |x(k)| \\ e_{\phi}(k) &= (\angle z(k) - \angle x(k)) \end{split}$$

where

$e_m(k)$ =magnitude error

$e_{\phi}(k)$ =phase error

z(k)=magnitude of feedback signal (signal 310)

6

x(k)=magnitude of input signal (signal 290)

$\angle z(k)$ =phase angle of feedback signal (signal 320)

$\angle x(k)$ =phase angle of input signal (signal 300)

For the magnitude LUT entries in the magnitude LUT block 220, two variables are defined and used in the process:

$$\delta_F = -\mu_F \cdot e_m(k)$$

where

$\delta_{E}$ =update quantity dependent on the differences between the magnitudes of the input signal and of the feedback signal

$\mu_F$ =an update speed parameter  $\mu$  (user selectable), typically  $\mu_F > 0$ .

Since the magnitude LUT has LUT entries, each entry is given an entry address of n with 0≤n≤N-1, N being the maximum number of entries in the internal magnitude LUT in the magnitude LUT block 220.

An interpolation distance s is defined as  $s=\alpha M-n$  where the magnitude LUT may provide a corrective value to the  $20 \text{ n} = |\alpha M|$  (or the largest integer value less than or equal to  $\alpha$ M), M=|x(k)|, and  $\alpha$  is a scaling value applied such that the magnitude range (e.g.  $0 \le M < 1$ ) is mapped to a table index range  $0 \le n \le (N-1)$ .

The table entries are thus updated using the following table address):

$$\begin{split} F_n(k+1) = & F_n(k) + (1-s) \cdot \delta_{F} i f f 0 \leq n \leq (N-1) \\ F_{n+1}(k+1) = & F_{n+1}(k) + (s) \cdot \delta_{F} i f f 0 \leq n + 1 \leq (N-1) \end{split}$$

where

$F_n(k)$ =table entry n for time sample k  $F_n(k+1)$ =table entry n for time sample k+1

$F_{n+1}(k)$ =table entry for n+1 for time sample k  $F_{n+1}(k+1)$ =table entry n+1 for time sample k+1

From the above equations, it should be clear that one, two or no entries in the internal magnitude LUT are updated depending on the value of aM. Thus, for this implementation, depending on the value of  $\alpha M$ , one of  $F_n$ and  $F_{n+1}$  is updated, both are updated, or neither is updated. Other implementations, depending on the circumstances and

bers of entries. For the phase LUT entires, an analogous process is used in the phase update block **260**. An update quantity is defined:

needs of the particular application, may update other num-

$$\delta_G{=}{-}\mu_G{\cdot}e_{\phi}(k)$$

where

60

$\delta_G$ =update quantity dependent on the differences between the phase angles of the input signal and of the system output signal

$\mu_G$ =an update speed parameter (user selectable) where  $0 \leq \mu_G < 1$

Using the parameter s as defined above for the magnitude LUT, the phase LUT entries can be updated using the following formulas:

$$G_n(k+1) = G_n(k) + (1-s) \cdot \delta_{G}iff \ 1 \le n \le (N-1)$$

$G_{n+1}(k+1) = G_{n+1}(k+1) + (s) \cdot \delta_{G}iff \ 1 \le n \le N$

Again, much like the magnitude LUT entry update process, the update process for the phase entries will, depending on the value of  $\alpha M$ , update one, two, or none of 65 the phase LUT entries.

It should be noted that LUT adaptation may involve updating more than two entries with some weighting

applied. As an example, the weighting may depend upon the distance of the LUT entry from the update point. The discussion herein is based upon the use of two entries and the use of an interpretation distance.

As an example of the above processes, a phase entry 5 update will be illustrated. For this example, the following values are assumed:

N=6 M≦1  $\alpha=5$  $x(k)=0.35 \exp(j\cdot 2\cdot 7)$  $z(k)=0.2 \exp(j\cdot 3\cdot 1)$  $\mu_G = 0.1$

Thus, M=0.35 and  $\alpha$ M=1.75. Thus, n=1 (since the lowest 15 integer value less than or equal to 1.75=1) and n+1=2. From these values, s=1.75-1=0.75. Given that  $z(k)=0.2 \exp(j\cdot 2.3)$ , the  $e_{\phi}(k) = -0.4$ . Thus,  $\delta_G = -(0.1)(-0.4) = +0.04$ . The require correction for G<sub>1</sub> is therefore

$(1-s) \cdot \delta_G = (1-0.75)(+0.04) = 0.25 \cdot (+0.04) = 0.01$ . For  $G_2$ , the <sup>20</sup> signal,  $x_\delta(k)$  is defined and this is ideally correction is  $s \cdot \delta_G = (0.75)(0.04) = 0.03$ . The new values are therefore:

$$G_1(k+1)=G_1(k)+0.01$$

$G_2(k+1)=G_2(k)+0.03$

This update is illustrated by the values in the following table:

| Address (n) | LUT content<br>before update | Correction | LUT content after update |

|-------------|------------------------------|------------|--------------------------|

| 0           | -1                           | 0          | -1                       |

| 1           | 2                            | 0.01       | 2.01                     |

| 2           | -0.5                         | 0.03       | -0.47                    |

| 3           | -0.5                         | 0          | -0.5                     |

| 4           | 0.5                          | 0          | 0.5                      |

| 5           | 2                            | 0          | 2                        |

It should be noted that the above process also takes into 40 account the lookup of values that are not to be found in the internal lookup tables. Linear interpolation using s=αM-n is used for magnitude values that cannot be found in the lookup table entries. As an example, if the magnitude is given as interpolation is used. The following formula is used to find values not found in the lookup tables:

$$F(M)=(1-s)\cdot F_n+s-F_{n+1}$$

where

F<sub>n</sub>=table value A

$F_{n+1}$ =table value B with the desired value being between table values A and B

$n=|\alpha M|$  (the largest integer value less than or equal to  $_{55}$  $\alpha M$ )

$s=\alpha M-n$

$\alpha$ =scaling value as defined above.

From the above discussion, it should be fairly clear that two of the values underpinning most of the calculations are 60 the values for  $e_m(k)$  and  $e_{\phi}(k)$ , the magnitude and phase errors. For proper synchronization between the relevant input signal and the relevant feedback signal (i.e. the tapped system output signal 345), the input signal must be properly delayed so that samples from the interpolated input 65 caded delay elements and associated sample storage. FIG. 5 waveform, as obtained from the delayed input signal samples, are mated with the relevant system output signal

8

sample. Such proper delaying should therefore take into account most, if not all, the time delay involved in the processing production, and feedback of the system output signal (round trip delay). This round trip delay is denoted as τ (seconds) and, before the LUT updating begins, the delay blocks 240, 270 acquires the delay and delays the input signal accordingly so as to time-align the input signal samples with the incoming feedback signal.

To implement this delay, a delay line is used with a depth 10 of K, meaning K samples of the input signals may be stored in the delay line. As should be clear, each of the K samples were sampled at different instances in time. The value of K is predetermined and should be enough to allow for the maximum possible path delay between the input signal and the feedback signal. These delays are due to a combination of any of the following: digital pipelining, analog and digital filter group delays, analog propagation delays, and the system and implementation dependent delays.

Because of this delay, a time delayed version of the input

$$x_{\delta}(k) = x(k-\delta)$$

where

$\delta = \tau \cdot F$

25

F<sub>s</sub>=signal sampling rate

$\tau$ =delay (normal trip delay between input and system output signal feedback)

To obtain a better result for  $x_{\delta}(k)$ , linear interpolation is  $_{-30}$  used to allow for fractional values of  $\delta$ . Thus, the delay is divided into two parts  $\kappa$ , the integer part of the sample (representing a discrete sample delay at the sample rate F<sub>s</sub>), and v, a fractional sample of the delay.

Using this notation, the delayed portion of the input signal 35 can be represented as:

$$x_{\delta}(k)=(1-v)\cdot x(k-\kappa)+v\cdot x(k-\kappa+1)$$

where  $\delta = \tau \cdot F$

$\kappa = |\delta|$  $\nu = \delta - \kappa$

50

As can be seen, for an integer  $\delta$ ,  $x_{\delta}(k)=x(k-\delta)$ .

The above Cartesian equation can be applied to polar 0.35 but the only table entries are 0.3 and 0.4, linear 45 representations by having separate delay lines for magnitude  $(|\mathbf{x}_{\delta}(\mathbf{k})|)$  and phase  $(\angle \mathbf{x}_{\delta}(\mathbf{k}))$  using the sequences  $|\mathbf{x}(\mathbf{k})|$  and  $\angle x(k)$ . These are given by:

$$\angle x_{\mathrm{d}}(k) {=} (1 {-} \mathbf{v}) {\cdot} \angle x(k {-} \mathbf{k}) {+} \mathbf{v} {\cdot} \angle x(k {-} \mathbf{k} {+} 1)$$

$$|x_{\delta}(k)| = (1-v)\cdot |x(k-\kappa)| + v\cdot |x(k-\kappa+1)|$$

It should be fairly clear that  $x_{\delta}(k)$  is calculated from the samples x(k), x(k-1), x(k-2), . . .  $x(k-\kappa)$ , samples of the input signal taken at time k, k-1, k-2, . . .  $k-\kappa$ .

The above equations for  $\angle x_{\delta}(k)$  has a peculiarity that is due to the way angle values work. Since  $\angle x(k-\kappa)$  and  $\angle x(k-\kappa+1)$  are represented by modulo  $2\pi$  radians (360) degrees) and since  $-\pi \le \angle x(k) \le \pi$ , then errors could easily occur.

Thus, if  $-\pi \le \angle x(k) \le \pi$ , and if  $|\angle x(k-\kappa+1) - \angle x(k-\kappa)| \ge \pi$ ,

$$\angle x_{\delta}(k) = (1-v) \cdot \angle x(k-\kappa) + v \cdot (\angle x(k-\kappa+1) + 2\pi, \text{ if } \angle x(k\kappa+1) \leq \angle x(k-\kappa)$$

The above described delay can be implemented by casillustrates such a delay subsystem which can be used as delay blocks 240, 270. As can be seen, delay elements 242A,

242B, 242C, 242D, 242E are cascaded and provide delays and storage for input signal samples 244A, 244B, 244C, 244D, 244E. Switches 245A, 245B, 245C, 245D, 245E allow any one of the signal samples 244A–244E to be switched so that it can be used. These samples 244A–244E can be weighted accordingly by programmable weighting blocks 246A, 246 B, 246C, 246D, 246E. The weighted samples are then summed up by adder 248 to produce the delayed signal 249 to be used by the system. The switches 245A . . . 245E and the values in the weighting blocks 246A . . . 246E may be user/system controllable so that any combination of weighted samples may be produced.

As an example, if  $\tau \cdot F_s = 2.4$  samples is required, then a value of 0.6 is used by the weighting block **246**C and a value of 0.4 is used by the weighting block **245**D. Then, by closing switches **245**C and **245**D then the sample x(k-2.4) is obtained.

The feedback signal (the tapped system output signal 345 which is a replica of the system output signal 110) may be further processed to achieve better results. As an example, the gain and/or phase of this replica of the system output 20 signal may be adjusted for better coordination with the delayed replica of the input signal.

Regarding the amplifier subsystem 10, FIG. 6 illustrates one embodiment of the subsystem 10. In FIG. 6, the signal decomposer 20 of FIG. 1 comprises a phasor fragmentation 25 engine 20A along with phase modulation units 60A, 60B. The fragmentation engine **20**A receives the magnitude (M) and phase (\$\phi\$) representing the predistorted signal. The phasor fragmentation engine 20A deconstructs a predetermined modulation waveform (the predistorted signal) into 30 signal components which are of equal and constant magnitude. Further information regarding the phasor fragmentation engines may be found in the applicant's co-pending application U.S. application Ser. No. 10/205,743 entitled COMPUTATIONAL CIRCUITS AND METHODS FOR 35 PROCESSING MODULATED SIGNALS HAVING NON-CONSTANT ENVELOPES, which is hereby incorporated by reference. In FIG. 6, these signal components are denoted by angles  $\alpha$  and  $\beta$ . These components are each received by RF modulation and filtering blocks 60A, 60B which process 40 the components to produce RF modulated and filtered versions of the components. The signal component 70A is an RF signal with phase a while signal component 70B is an RF signal with phase  $\beta$ . These components 70A, 70B are then amplified by amplifiers 90A, 90B. The amplified compo- 45 nents are then recombined using combiner 100. It should be noted that the phase modulation, also known as carrier modulation, may also introduce some undesired amplitude modulation. Signal decomposition methods other than the phasor fragmentation referred to above may also be used by 50 the signal decomposer 20.

Regarding the Chireix architecture amplifier subsystem 10, it has been found that, for higher amplification efficiencies, switch mode amplifiers are preferred for the amplifiers 90A, 90B. Such switch mode amplifiers, specifically Class D and Class F power amplifiers, provide low output impedances that allow higher amplification efficiencies. A co-pending application filed on Oct. 16, 2002 and having U.S. Ser. No. 10/272,725 entitled CHIREIX ARCHITECTURE USING LOW IMPEDANCE AMPLIFIERS 60 provides further information on the desirable components and is hereby incorporated by reference. Such types of amplifiers are not required for the invention to function but they have been found to provide performance at a desirable level.

It should further be noted that while those are only two parallel amplifiers 90A, 90B in FIG. 1 and FIG. 6, multiple

10

parallel amplifiers may be used as long as the decomposer 20 decomposes the predistorted signal 130 into enough components so that each component is separately amplified and phase modulated in parallel with the other components.

It should also be noted that the predistortion subsystem 10 explained above does not linearize a power amplifier as is well-known in the field. Instead, the predistortion subsystem linearizes a whole power amplifier system—the output of the whole amplifier system is linearized and not simply the output of a single amplifier. Also, unlike the linearizing systems for power amplifiers that are currently known, the amplifier system discussed in this document compensates for distortions that mostly occur at mid signal amplitudes. Current single amplifier linearization systems linearize distortions that occur at large signal amplitudes.

It should further be noted that the invention may be applied to any signal processing system which decomposes a signal into components and recombines them. It has been found that signal combiners (block 100 in FIG. 1) invariably cause distortions. These combiners use addition to recombine the components and improper signal addition, such as when recombining sinusoidal components, has been found to be one cause of the distortions in the system output signal. In the above embodiment, the phasor fragmentation engine decomposes the incoming signal into vectors and the improper addition of these vectors by the combiner 100 lead to distortions in the output signal.

While the above embodiment amplifies the input signal, albeit separately for each component, this need not be the only signal processing accomplished after the input signal is decomposed. Referring to FIG. 7, such a generalized system (which could be part of a larger signal transmission system) is illustrated. The predistortion subsystem 120 predistorts an incoming signal 30 and compensates for distortions introduced in the system output signal 110 by the improper or imperfect recombining of the input signals components. These components are produced by the signal decomposer 20 and are separately processed by signal component processor blocks 75A, 75B. The processing executed by the blocks 75A, 75B may take the form of amplification (as in the embodiment above), phase modulation, a combination of the two, or any other signal processing which may be desired. As an example, each of the signal components illustrated in FIG. 6 may be separately phase modulated in addition to being amplified by amplifiers 90A-90B. The phase modulation may be accomplished separately or be incorporated in the signal decomposer or, as contemplated for the implementation illustrated in FIG. 6, incorporated into the modulation and filtering blocks 60A, 60B.

As can be seen in FIG. 7, the signal processing subsystem 10A receives the predistorted signal from the predistortion subsystem 120. After being received, the predistorted signal is decomposed by the signal decomposer 20 into components. These components are then separately processed by the signal component processor blocks 75A, 75B and are then recombined by the recombiner 100.

A feedback signal processing block 400 receives a portion of the system output signal 110 and processes this portion so it may be used by the adaptive predistortion subsystem 120. As an example, the feedback signal processing block 400 may contain the A/D converter 330, the conversion unit 340, the filtering module 337, and the demodulation module 335 illustrated in FIG. 4. The same block 400 may also contain processing blocks 410, 420 for adjusting the magnitude and/or phase of the feedback signal.

One advantage using the above invention is that it allows less stringent tolerances to be used for the system compo-

nents. Previously, components had to be substantially matched so that signal processing could produce acceptable results. By using the above invention, less than substantially matched components may be used together. Errors due to a mismatch may be measured and compensated for by the 5 predistortion subsystem.

Referring to FIG. 8, a detailed block diagram of a system incorporating the features illustrated in FIGS. 3, 4 and 7 is presented. As can be seen, the adaptive predistortion block 120 in FIG. 8 is comprised of the separate magnitude delay 10 240 and phase delay 270 along with a magnitude predistortion calculation block 260A. The inputs of these calculation blocks 230A, 260A are the delayed input signals from the delay blocks 240, 270 and the adjusted feedback signals from the feedback signal processing block 400. After the magnitude and phase predistortion modification are calculated, then the magnitude LUT block 220A and the phase LUT block 250A apply the predistortions. It should be noted that the magnitude LUT block 220A includes the magnitude LUT 220 and the magnitude LUT update block 20 230 shown in FIG. 3. Similarly, the phase LUT block 250A incorporates the phase LUT 250 and the phase LUT update block 260 illustrated in FIG. 3.

As can also be seen, the feedback signal processing block 400 illustrated in FIG. 7 is comprised of the Cartesian to 25 polar coordinate conversion block 340, the filtering module 337, and the demodulation module 335. Also included in the feedback signal processing block 400 are the magnitude and phase adjustment blocks 410, 420.

A person understanding this invention may now conceive 30 of alternative structures and embodiments or variations of the above all of which are intended to fall within the scope of the invention as defined in the claims that follow.

What is claimed is:

- 1. A system for processing an input signal, the system 35 comprising:

- an adaptive predistortion subsystem for receiving said input signal and for producing a predistorted signal by applying a deliberate predistortion to said input signal, wherein said deliberate predistortion includes magnitude distortions which adjust a magnitude of said input signal; and

- a signal processing subsystem receiving and processing said predistorted signal and producing a system output signal,

# wherein

- said adaptive predistortion subsystem distorts said Input signal to compensate for distortions in said system output signal;

- said signal processing subsystem decomposes said predistorted signal into separate components, each of said separate components being processed separately;

- said processing subsystem combines said components after processing to produce said system output signal; 55

- said deliberate predistortion applied to said input signal by said adaptive predistortion subsystem to produce said predistorted signal is adjusted based on said system output signal.

- 2. A system according to claim 1 wherein said signal processing subsystem comprises:

- a signal decomposer for decomposing said predistorted signal into at least two components;

- at least two signal component processor blocks, each 65 signal processor block receiving an output of said signal decomposer and each signal processor block

12

- separately processes said output received from said signal decomposer; and

- a combiner receiving a processed output from each of said at least two signal component processor blocks, said combiner producing said system output signal from said processed outputs of said at least two signal component processor blocks.

- 3. A system according to claim 2 wherein at least one of said at least two signal component processor blocks includes an amplifier.

- **4.** A system according to claim **3** wherein said amplifier is a non-linear amplifier.

- 5. A system according to claim 1 wherein said system is part of a signal transmission system.

- **6**. A system according to claim **1** wherein at least some of said distortions are due to said combiner.

- 7. A system according to claim 3 wherein said amplifier is a switch mode amplifier.

- **8**. A system according to claim **3** wherein said amplifier has a low output impedance.

- **9**. A system according to claim **1** wherein said deliberate predistortion is based on at least one entry in a lookup table.

- 10. A method of processing an input signal to produce a system output signal, the method comprising:

- a) receiving said input signal and accessing an entry in a lookup table;

- applying a deliberate predistortion to said input signal to result in a predistorted signal, said deliberate predistortion being based on said entry;

- c) decomposing said predistorted signal into at least two component signals;

- d) combining said at least two component signals to produce said system output signal;

- e) adjusting said deliberate predistortion based on said system output signal; and

- f) updating at least one entry in said table.

- 11. A method according to claim 10 wherein said system output signal is an RF modulated version of said input signal.

- 12. A method according to claim 10 further including a processing step of separately processing each of said at least two component signals prior to step d).

- 13. A method according to claim 12 wherein said processing step includes amplifying at least one of said at least two component signals.

- 14. A method according to claim 12 wherein said processing step includes phase modulating at least one of said at least two component signals.

- 15. A method according to claim 10 wherein said deliberate predistortion is based on an interpolation of entries in said table.

- **16**. A system according to claim **1** wherein said predistortion subsystem receives a replica of said system output signal.

- 17. A system according to claim 2 wherein said deliberate predistortion is dependent on differences between said input signal and said replica of said system output signal.

- 18. A system according to claim 9 wherein entries in said lookup table are periodically updated based on characteristics of a replica of said system output signal.

- 19. A system according to claim 9 wherein said deliberate predistortion is based on an interpolation of entries in said table.

- 20. A system according to claim 1 wherein said predistortion subsystem includes:

- determining means for determining said deliberate predistortion;

- adjustment means for applying said deliberate predistortion to said input signal;

- update means for periodically updating said determining means based on said system output signal.

- 21. A system according to claim 20 wherein said adjustment means receives parameters of said deliberate predistortion from said determining means.

- 22. A method according to claim 10 further including the step of taking a difference between said input signal and a replica of said system output signal to determine said characteristics of said system output signal.

- 23. An adaptive predistortion subsystem for use with a signal processing system which produces a system output signal, the predistortion subsystem comprising:

- determining means for determining a deliberate predistortion to be applied to an input signal, said determining means comprising

- a lookup table having entries, said entries being used to determine said deliberate predistortion and

- an interpolating means for determining values not <sup>20</sup> found in said lookup table;

- adjustment means for applying said deliberate predistortion to said input signal; and

- update means for periodically updating said determining 25 means based on characteristics of said system output signal.

- 24. An adaptive predistortion subsystem according to claim 23 wherein said adjustment means receives parameters of said deliberate predistortion from said determining 30 means.

- 25. An adaptive predistortion subsystem according to claim 23 wherein said determining means comprises a lookup table having entries, said entries being used to determine said deliberate predistortion.

- 26. An adaptive predistortion subsystem according to claim 23 wherein said deliberate predistortion is dependent on differences between said input signal and said replica of said system output signal.

- **27**. A method according to claim **10** wherein said deliberate predistortion is at least partially based on characteristics of said system output signal.

- **28**. A method according to claim **27** wherein said deliberate predistortion is determined in an iterative manner during transmission of said system output signal.

- **29**. A system according to claim **1** wherein said predistorted signal is adjusted based on said system output signal and said input signal.

- **30**. A method according to claim **10** wherein for step e), said deliberate predistortion is adjusted based on said system output signal and said input signal.

- 31. A system according to claim 23 wherein said update means periodically updates said determining means based on said system output signal and said input signal.

- **32.** A system for processing an input signal, the system comprising:

14

- an adaptive predistortion subsystem for receiving said input signal and for producing a predistorted signal by applying a deliberate predistortion to said input signal, wherein said deliberate predistortion includes phase distortions which adjust a phase of said input signal; and

- a signal processing subsystem receiving and processing said predistorted signal and producing a system output signal,

10 wherein

- said adaptive predistortion subsystem distorts said Input signal to compensate for distortions in said system output signal;

- said signal processing subsystem decomposes said predistorted signal into separate components, each of said separate components being processed separately;

- said processing subsystem combines said components after processing to produce said system output signal; and

- said deliberate predistortion applied to said input signal by said adaptive predistortion subsystem to produce said predistorted signal is adjusted based on said system output signal.

- 33. A system according to claim 32 wherein said signal processing subsystem comprises:

- a signal decomposer for decomposing said predistorted signal into at least two components;

- at least two signal component processor blocks, each signal processor block receiving an output of said signal decomposer and each signal processor block separately processes said output received from said signal decomposer; and

- a combiner receiving a processed output from each of said at least two signal component processor blocks, said combiner producing said system output signal from said processed outputs of said at least two signal component processor blocks.

- **34**. A system according to claim **33** at least one of said at least two signal component processor blocks includes an amplifier.

- 35. A system according to claim 34 wherein said amplifier is a non-linear amplifier.

- **36**. A system according to claim **22** wherein said system is part of a signal transmission system.

- 37. A system according to claim 32 wherein at least some of said distortions are due to said combiner.

- **38**. A system according to claim **32** wherein said amplifier is a switch mode amplifier.

- **39**. A system according to claim **34** wherein said amplifier has a low output impedance.

- **40**. A system according to claim **32** wherein said deliberate predistortion is based on at least one entry in a lookup table

\* \* \* \* \*